- 您现在的位置:买卖IC网 > Sheet目录1250 > TURBO-DECO-XM-UT3 (Lattice Semiconductor Corporation)SITE LICENSE TURBO DECODER XP

�� �

�

Lattice� Semiconductor�

�Turbo� Decoder� User’s� Guide�

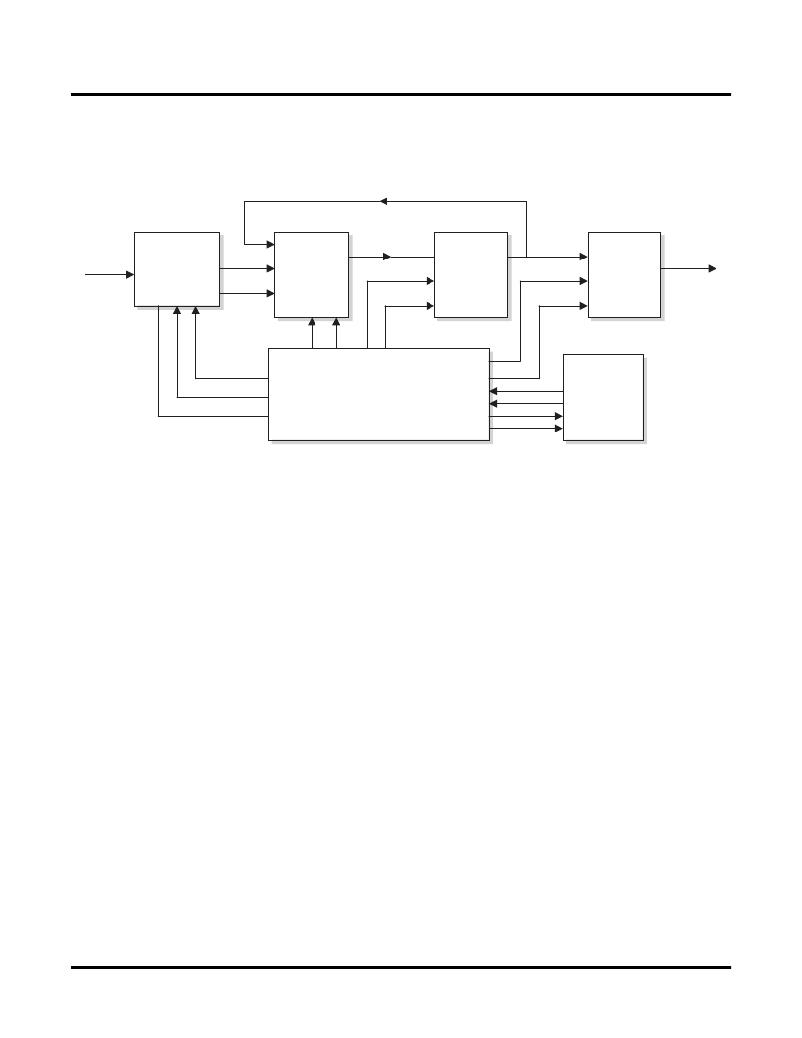

�Block� Diagram�

�Figure� 2� shows� a� block� diagram� of� the� Turbo� Decoder� detailing� the� key� components� and� the� data� paths� between�

�these� blocks.�

�Figure� 2.� Turbo� Decoder� Functional� Block� Diagram�

�Map�

�LLR�

�Hard�

�Decision�

�Storage�

�din�

�Data/Parity�

�Memory�

�Memory�

�Data�

�Parity�

�Map�

�Decoder�

�Decoder�

�write� address�

�write� enable�

�LLR�

�Buffer�

�Buffer�

�write� address�

�write� enable�

�Hard�

�Decision�

�Storage�

�(optional)�

�dout�

�(optional)�

�write address�

�read� address�

�Control�

�Interleaver�

�write� enable�

�Functional� Description�

�The� Turbo� Decoder� consists� of� four� main� components:� control� module,� decoder,� interleaver� and� memory� buffers.�

�Control� Module�

�The� control� module� takes� care� of� the� interface,� pipelining� and� handshake� communication� between� various� blocks�

�and� I/O� pins.� Data� and� parity� are� read� serially� into� the� memory� and� it� is� assumed� that� the� data� is� received� in� the�

�same� order� as� it� was� transmitted� from� the� encoder.� Signal� blocksizeset(ipcfgset)� initializes� the� blocksize�

�by� specifying� the� size� of� the� block� to� be� input� to� the� decoder.� Input� data� can� be� given� only� when� rfi� is� asserted.�

�Input� data� has� to� be� quali?ed� with� inpvalid� to� be� accepted� by� the� core.�

�Decoder� and� Interleaver�

�Once� the� data� is� entered� into� the� decoder,� the� decoder� starts� computing� the� LLR� of� each� data� symbol.� The� LLR� is�

�computed� for� the� block� sequence� twice,� once� using� the� non-interleaved� data� and� the� corresponding� parity� and� then�

�using� the� interleaved� data� and� the� corresponding� parity.� One� round� of� this� computation� is� called� an� iteration.� Each�

�iteration� is� divided� into� two� sections,� an� ODD� window� and� an� EVEN� window.� The� LLR� for� systematic� parity� is� com-�

�puted� during� the� ODD� window� and� the� LLR� for� interleaved� data� is� computed� during� the� EVEN� window.� When� both�

�ODD� and� EVEN� window� computations� are� done,� one� iteration� is� complete.� The� user� can� set� the� number� of� itera-�

�tions� for� each� block� on� the� iterations� pin.� During� the� second� half� of� the� iteration,� EVEN� window,� the� LLR� computed�

�in� the� ?rst� half� is� improved� upon� by� using� previous� computations.� Every� window� makes� use� of� LLR� information�

�computed� in� the� previous� window� and� tries� to� improve� on� the� estimate� of� LLR.� The� interleaver� is� used� in� the� second�

�half� of� iteration� to� generate� the� interleaved� address.� This� address� is� used� to� address� the� data� and� parity� memory� to�

�read� the� interleaved� data� for� the� second� half� of� the� iteration.� It� is� also� used� to� address� the� LLR� memory� unit� and� get�

�the� previously� computed� LLR� information.� At� the� end� of� one� iteration,� the� decoder� has� a� set� of� LLR� for� each� input�

�data.� The� second� iteration� starts� with� again� using� the� non-interleaved� parity� bits� and� data� and� the� previously� com-�

�puted� LLR� to� get� a� new� estimate� of� the� LLR� for� the� data.� Once� the� decoder� completes� the� number� of� iterations�

�required� to� be� done,� the� LLR� memory� buffer� has� the� ?nal� LLR� values.� The� sign� of� the� LLR� values� determines�

�whether� the� data� is� a� ‘1’� or� a� ‘0’.� A� positive� sign� means� the� data� value� is� a� ‘1’,� otherwise� it� is� a� ‘0’.�

�4�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

TVB058SA-L

SURGE PROTECTOR 58V DO-214AA

TVB200SA-L

SURGE PROTECTOR 200V BREAKOVER

TVB200SC-L

SURGE PROTECTOR 200V BREAKOVER

TVB270SB-L

SURGE PROTECTOR 270V DO-214AA

TVB270SC-L

SURGE PROTECTOR 270V DO-214AA

TVB300SA-L

SURGE PROTECTOR 300V DO-214AA

TVB300SB-L

SURGE PROTECTOR 300V DO-214AA

TVB300SC-L

SURGE PROTECTOR 300V DO-214AA

相关代理商/技术参数

TURBO-DECO-XP-N1

功能描述:编码器、解码器、复用器和解复用器 Turbo Decoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray

TURBO-ENCO-E2-U3

功能描述:编码器、解码器、复用器和解复用器 Turbo Encoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray

TURBO-ENCO-O4-N1

功能描述:编码器、解码器、复用器和解复用器 Turbo Encoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray

TURBO-ENCO-P2-U3

功能描述:编码器、解码器、复用器和解复用器 Turbo Encoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray

TURBO-ENCO-PM-U3

功能描述:开发软件 Turbo Encoder RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

TURBO-ENCO-SC-U3

功能描述:编码器、解码器、复用器和解复用器 Turbo Encoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray

TURBO-ENCO-X2-U3

功能描述:开发软件 Turbo Encoder RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

TURBO-ENCO-X2-UT3

功能描述:开发软件 TURBO ENCODER RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors